# **Probe Card Metrology** "Challenges and Solutions"

Jim Powell, Applications Engineer Rudolph Technologies

## Agenda

- **1**. Overview

- 2. Cost of Ownership

- 3. Probe Card Metrology

- 4. Top Challenges

- 5. Probe Card Circuit Control

- 6. Fine Pitch/Small Probe Tips

- 7. Planarity Methods

- 8. Alignment Methods

- 9. Probe Card Interfaces

- **10**. Conclusion

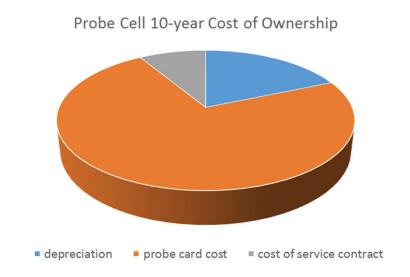

## Probe Cell Cost of Ownership

Based on typical baseband processor and logic ATE

Advanced Probe Card is the majority of Probe Cell CoO

- Achieving acceptable Cost of Test has driven costs to the probe card

- Increased parallelism

- On-board electronics

- Short product life-cycle of consumer electronics

Maintaining probe cards extends life and improves CoO

## **Probe Card Metrology**

Extending the life of probe cards improves the CoO

Use of Probe Card Metrology is essential to:

- Assure the quality of the probe card at manufacture

- Achieve production efficiencies

- Site-to-site correlation

- Production reliability

- Ease of probe card cleaning, repair and maintenance

- And most importantly verifies probe card test capability outside the test cell

## Challenges

#### Well understood... harder to achieve

#### Process geometries, larger arrays, and increasingly complex electronic circuitry

- Advanced Probe Card Circuitry

- Fine Pitch/Small Probe Tips

- Smaller, finer probes require

- Improved stage accuracy and camera resolution

- More test device sizes

- Planarity Measurements Z position

- Loaded vs Unloaded

- Alignment Measurement XY position

- Single image capture vs traditional dual image

- Continuous scan

- Probe Card Interfaces

- Full Emulation (PCI) vs Low Cost Holder (PCH)

#### Overview

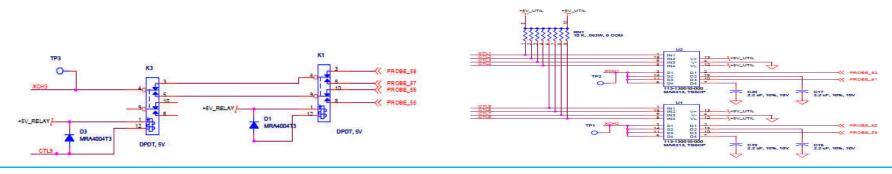

- Probe cards over the past decade have been increasingly required to perform more and more advanced circuit control such as: switching, multiplexing, and on-board signal generation.

- Many of these control circuits complicate or prevent the measurement of individual probes, for electrical and physical properties.

- As the demands have changed, so have the available solutions. Over the next few slides we'll

discuss solutions that have been available in the past, the current available solutions and some

of the upcoming solutions to Circuit Control and Probe Card Metrology.

COMP/SS 2017

#### **Previous Solutions**

- Legacy tools, PrecisionPoint VX3 and ProbeWoRx300 included exclusive power channels for powering probe card devices.

- These power channels required very specific trace locations, and limited their flexibility based on Probe Card Interface (PCI) design.

- Another short-coming of this approach was the single switching capability, meaning that the power channel could be defined as "on" or "off" in a single recipe

- If a probe card needed multiple switching, multiple recipes were needed.

- The PWX300 added the capability of performing optical-based or gram-force planarity, which provided measurement for probes electrically isolated or in unsupported configurations.

COMP/SS 2017

#### **Present Solutions**

- Our current probe card tool the PrecisionWoRx VX4, provides legacy power channels for backward capability, as well as combo signal/power channels for all other probe card connections.

- The combo channels are able to perform normal probe electrical measurements as well as provide power to probe card components.

- Channel power is controlled by state definitions, and allows power to be switched on and off in multiple combinations, for individual probe and for component testing.

| 5.000 V<br>12.000 V |                         | RiyPw<br>CTL3<br>CTL2<br>CTL3 |               | Channel Label G                        |            | Roat Orannel Label<br>CTL3,CTL2,CTL1 | Delay Tim |

|---------------------|-------------------------|-------------------------------|---------------|----------------------------------------|------------|--------------------------------------|-----------|

|                     |                         |                               |               |                                        |            |                                      |           |

| Diele Ciele ind     | Edit Chargani I         |                               |               |                                        |            |                                      |           |

|                     | Provide statements      | eres                          |               | 1                                      |            |                                      | 1         |

| TA I                | Power: B<br>samefiLabel | Ground<br>Channel Labe        | e Chamellabel | Delay Times<br>{ extinction (seconds ) | StateLabel | Connents                             |           |

| A 1                 | samel Label             |                               | e ChameiLabel | Delay Times<br>(indisconds.)           | 5T_DEFAULT |                                      |           |

| A 1                 | samel Label             | Channel Labe                  | e ChamelLabel | Delay Tens<br>( edieconds )            |            |                                      |           |

|                     |                         |                               | e             |                                        |            |                                      |           |

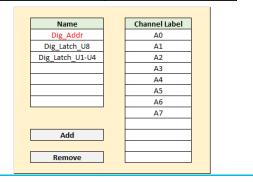

#### **Upcoming Solutions**

- In the near future, new *Enhanced State Control* software will be available for the VX4 tool and the next generation tool.

- The new capabilities are to include:

- Multiple voltage support

- State Sequencing

- User pause

- Debugging/stepping through activation states

- External power supply support

| Name       | Power/Logic State | Delay (msec) | Comment    |

|------------|-------------------|--------------|------------|

| ST_Default | Pwr_2             |              |            |

| ST_1       | Log_2             | USER_PAUSE   |            |

| ST_2       |                   |              | EXIT_STATE |

|            | Log_2_exit        |              |            |

|            | Pwr_2_exit        |              |            |

|            |                   |              |            |

|            |                   |              |            |

|            |                   |              |            |

|            |                   |              |            |

| Add        |                   |              |            |

|            |                   |              |            |

| Remove     |                   |              |            |

#### External Supply Definition

| PS_Ext1 | -15 |

|---------|-----|

| PS_Ext2 | -5  |

## Fine Pitch – Small Probe Tips

#### **Problems**

Process nodes  $\rightarrow$  smaller die pads  $\rightarrow$  tighter pitch

Increased demand for positional accuracy

#### **Solutions**

High resolution optics

Camera pixel size equivalence of ~0.25µ for probe tips ≤5µ

High accuracy stage

Current: 3.5 microns at 3 sigma

2018: ~1µ

Checkplate isolation dot, and posts @ 25µ are available

COMP/SS2017

## **Planarity Methods**

Probe card planarity measurements are essential to verify that the probe card plane will match the plane of the wafer. Most commonly probe Z positions are measured electrically, by moving a conductive device in contact with the probe to determine its position.

- This type of measurement can be preformed with a plate, which will overdrive many probes at the same time, finding continuity based on channel connections, and puts a loading force on the probe card similar to a wafer in a prober stage.

- Alternatively a fine conductive post can be used to find individual probe planarity without applying a load the probe card.

- Differences between these methods can be attributed to things like:

- probe card deflection

- PCI stiffness

- Stage compliance

### **Planarity Methods**

#### **Loaded Planarity**

#### Advantages

- Emulation similar to test conditions of wafer overdrive

- Speed non-bussed probes can be measured within a single contact

#### Disadvantages

- Deflection can skew results, depending on PC, PCI and stage deflection components

- Wear bussed probes tested at isolation dots require the entire probe card to be overdriven

- Data matching bussed and non-bussed probes are tested on different surfaces and the data points must be calibrated and synchronized.

#### **Unloaded Planarity**

#### Advantages

- Single device all probes are measure at post, syncing with checkplate isn't needed

- Planarity, CRes, Probe Force, Primary Channel can all be measured during a single contact

- No deflection testing single probes require very little force, lower \$\$\$ PCI can be employed

- Force method planarity can be measured by gram force, without electrical connection.

- A Probe Card Holder (PCH) can be used instead of PCI

#### Disadvantages

- Slower probes must be measured one at a time

- Non-emulating –doesn't always match test cell test conditions

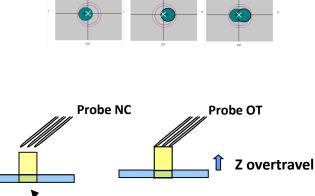

## **Alignment Methods**

Alignment measurements are taken optically from a precision XY stage, these measurements are taken to ensure the probe position will match the position of the wafer pad

- Traditional alignment method

- Two sets of images from free hanging and an overdriven position

- Alternative methods

- Single image capture

- Free Hanging, Center, or Overdrive position

- Greater speed, and only supplies data that is needed

- High Speed Continuous optical scanning

- Next generation tool

**`Optical window (field of view)**

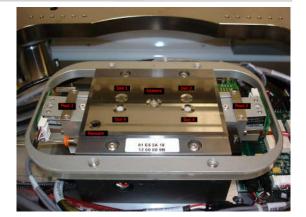

## **Probe Card Interfaces**

The purpose of a Probe Card Interface (PCI) is to provide a mechanical and electrical adaptation from the metrology tool to the probe card

- Full Emulation

- PCI's can be provided the emulate the test cell as closely as possible using the exact same componentry as the prober interfaces. These types are the highest in cost but the best in representing the structure of the test cell.

- Lite versions

- Many lower cost solutions are also available that make use of our No-Load test capabilities. These use low force methods for securing the probe card but still provide full electrical connectivity.

- Probe Card Holder

- For first article, R&D or "one off" probe cards, simple probe card holders can also be used, without electrical connections, and still provide measurement capabilities.

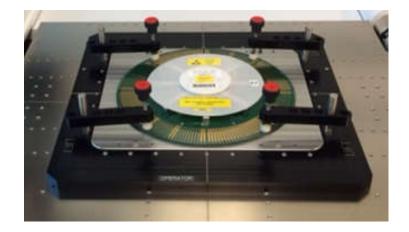

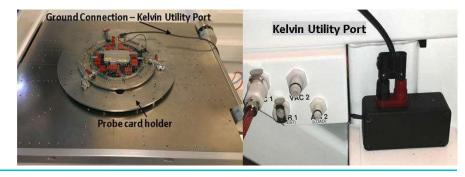

## **Probe Card Interfaces**

#### **Non-electrical Probe Card Holders**

Very low cost probe card holders can provide very basic test functionality, these can range from very simple plates that provide a surface to clamp the probe card to a custom universal probe card holder for easier usage

- Probe Card Holders

- Tests, Planarity, Alignment, Probe Force, and User Assisted Contact Resistance.

- Zero Channels needed

- Kelvin Port

- An external connection port on the tool allows for manual connection to probe traces.

## Conclusions

- The cost of owning a Probe Card metrology tools is one of the best Cost of Ownership (CoO) items in the probe cell.

- The challenges in probe metrology continue to evolve.

- Process shrinks higher precision needed

- Advanced circuitry control and test

- Advanced test methods

- Supporting every major probe technology in the world

- Probe Card Interfaces

- Full OEM emulation to low cost probe card holders

- Rudolph is committed to supporting, the probe industry now and far into the future, with new technology and tools!

### **COMP**\**SS** 2017

## **Thank You!**

# For questions, please contact: Jim Powell Rudolph Technologies Jim.Powell@rudolphtech.com